Research Breakthrough on Cryogenic CMOS ASICs for Superconducting Quantum Computing Systems

2023/12/08

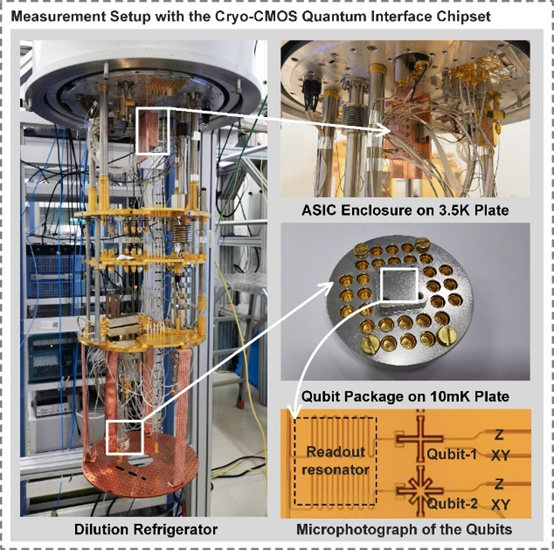

The Quantum Cloud group at BAQIS and School of Integrated Circuits at Tsinghua University have made a major breakthrough on cryogenic CMOS quantum interface chipsets for large-scale integration in quantum computing systems. The collaboration team have successfully fabricated a fully integrated cryogenic dual-qubit interface chipset using CMOS technology. This groundbreaking work, entitled "A Cryo-CMOS Quantum Computing Unit Interface Chipset in 28nm Bulk CMOS with Phase-Detection based Readout and Phase-Shifter based Pulse Generation", has been accepted for presentation at 2024 IEEE International Solid-State Circuits Conference (ISSCC) which will be held next February in San Francisco, CA, USA.

As research on scalable quantum computing progresses, qubit manipulation and readout chips that can effectively operate in cryogenic environments are considered the key enabling technology for practical, large-scale quantum computing. The core challenge of this technology involves enhancing the controlling/readout channels of qubit interface chips under the constraints of limited cooling power. To overcome this technical challenge and propel the miniaturization and integration of quantum computers forward, it is of significant importance to conduct research aimed at breaking through the design constraints of ultra-low-power qubit interface chips.

Based on previous research on the cryogenic characterization of CMOS devices and highly-integrated qubit control chip, the research team have designed a dual-qubit interface chipset (including the complete controlling and readout functionalities) with remarkably low power consumption. This chipset is based on the polar modulation and reflected readout technology using the phase-domain signal processing. It can generate the XY pulse signals, Z bias signals, and readout stimulating signals required for the controlling and readout of dual superconducting qubits at a 3.5K environment. Furthermore, the chipset also integrates a qubit state detection circuit, an on-chip clock generation and an instruction memory. Compared to the other state-of-the-arts designs, the chipset has achieved a significant improvement in reduction of power consumption. With the chipset, the research team has successfully realized effective controlling and readout of superconducting qubits.

The primary contributors to this work include Prof. Tiefu Li and Senior Research Staff Dr. Qichun Liu from Quantum Cloud group at BAQIS, and Dr. Yanshu Guo, Yaoyu Li, Wenqiang Huang, Tian Tian, Nan Wu, Siqi Zhang, Prof. Ning Deng, Prof.Zhihua Wang, and Associate Prof. Hanjun Jiang from the School of Integrated Circuits at Tsinghua University. This work was supported in part by the National Natural Science Foundation of China.

The International Solid-State Circuits Conference (ISSCC), organized by the IEEE Solid-State Circuits Society (SSCS), is widely recognized as the premier conference in the field of integrated circuit design. Established in 1953, ISSCC is typically the first venue for the international debut of cutting-edge solid-state circuit technologies during different periods. Many landmark inventions in the history of integrated circuits are initially disclosed at this conference. It attracts over 3,000 participants annually from the academic and industrial sectors worldwide.

中文

中文 Email

Email QCloud

QCloud Log in

Log in